第8章 MCS-51硬體模式

### I/O埠3的副功能

| 埠位元  | 副功能              |

|------|------------------|

| P3.0 | RxD (串列輸入埠)      |

| P3.1 | TxD (串列輸出埠)      |

| P3.2 | INTO (外部中斷輸入 0)  |

| P3.3 | INT1 (外部中斷輸入 1)  |

| P3.4 | T0 (定時器 0 外部輸入)  |

| P3.5 | T1(定時器1外部輸入)     |

| P3.6 | WR (外部資料記憶器寫入控制) |

| P3.7 | RD (外部資料記憶器讀取控制) |

林銘波編著 --- 全華科技圖書公司

8.7

林銘波編著 --- 全華科技圖書公司

第8章 MCS-51硬體模式

### MCS-51的外加時脈信號之時序參數值(AT89C51)

| 符號                  | 參數    | 最小値  | 最大値 | 單位  |

|---------------------|-------|------|-----|-----|

| 1/t <sub>CLCL</sub> | 時脈頻率  | 0    | 24  | MHz |

| t <sub>CLCL</sub>   | 時脈週期  | 41.6 |     | ns  |

| t <sub>CHCX</sub>   | 高電位期間 | 15   |     | ns  |

| t <sub>CLCX</sub>   | 低電位期間 | 15   |     | ns  |

| t <sub>CLCH</sub>   | 上升時間  |      | 20  | ns  |

| t <sub>CHCL</sub>   | 下降時間  |      | 20  | ns  |

林銘波編著 --- 全華科技圖書公司

8.9

#### 微算機基本原理與應用

第8章 MCS-51硬體模式

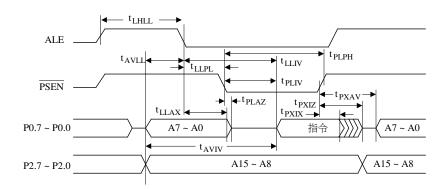

### MCS-51外部程式記憶器讀取週期時序圖

林銘波編著 --- 全華科技圖書公司

第8章 MCS-51硬體模式

## AT89C51外部程式記憶器讀取週期之時序參數值 (12與24 MHz)

| <i>የተ</i> ባው      | <b>允</b> 申标         | 12 N | ИHz | 24 N | 開冶  |    |

|-------------------|---------------------|------|-----|------|-----|----|

| 符號                | 參數                  | 最小値  | 最大値 | 最小値  | 最大値 | 單位 |

| $t_{LHLL}$        | ALE 脈波寬度            | 127  |     | 43   |     | ns |

| t <sub>AVLL</sub> | 位址成立到 ALE 爲低電位      | 28   |     | 28   |     | ns |

| $t_{LLAX}$        | ALE 爲低電位後的位址持住時間    | 48   |     | 21   |     | ns |

| $t_{LLIV}$        | ALE 爲低電位到成立的指令輸入    |      | 233 |      | 101 | ns |

| $t_{LLPL}$        | ALE 爲低電位到 PSEN 爲低電位 | 43   |     | 28   |     | ns |

| $t_{PLPH}$        | PSEN 脈波寬度           | 205  |     | 104  |     | ns |

| t <sub>PLIV</sub> | PSEN 爲低電位到成立的指令輸入   |      | 145 |      | 80  | ns |

| $t_{PXIX}$        | PSEN 爲低電位後的指令持住時間   | 0    |     | 0    |     | ns |

| $t_{PXIZ}$        | PSEN 爲低電位後到指令變爲浮接   |      | 59  |      | 31  | ns |

| $t_{PXAV}$        | PSEN 爲低電位到成立的位址     | 75   |     | 33   |     | ns |

| $t_{AVIV}$        | 位址到成立的指令輸入          |      | 312 |      | 153 | ns |

| $t_{PLAZ}$        | PSEN 爲低電位到位址變爲浮接    |      | 10  |      | 10  | ns |

林銘波編著 --- 全華科技圖書公司

第8章 MCS-51硬體模式

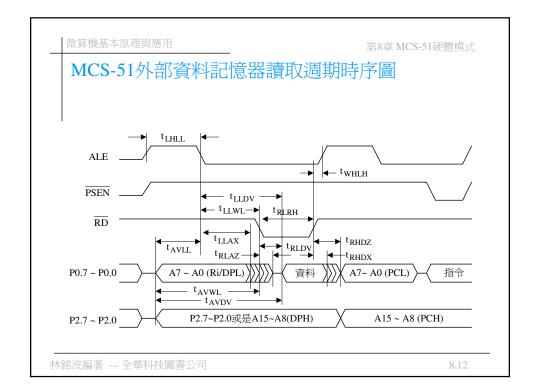

# AT89C51外部資料記憶器讀取週期之時序參數值 (12與24 MHz)

| 符號             | 參數                     |     | ИHz | 24 N | ИHz | 單位 |

|----------------|------------------------|-----|-----|------|-----|----|

| 付號             | 参数                     | 最小値 | 最大値 | 最小値  | 最大値 | 単位 |

| $t_{LHLL}$     | ALE 脈波寬度               | 127 |     | 43   |     | ns |

| $t_{AVLL}$     | 位址成立到 ALE 爲低電位         | 28  |     | 28   |     | ns |

| $t_{LLAX}$     | ALE 爲低電位後的位址持住時間       | 48  |     | 21   |     | ns |

| $t_{RLRH}$     | RD 脈波寬度                | 400 |     | 150  |     | ns |

| $t_{\rm RLDV}$ | RD 爲低電位到成立的資料輸入        |     | 252 |      | 118 | ns |

| $t_{\rm RHDX}$ | RD 爲高電位後的資料持住時間        | 0   |     | 0    |     | ns |

| $t_{RHDZ}$     | RD 爲高電位後到資料變爲浮接        |     | 97  |      | 55  | ns |

| $t_{LLDV}$     | ALE 爲低電位到成立的資料輸入       |     | 517 |      | 183 | ns |

| $t_{\rm AVDV}$ | 位址到成立的資料輸入             |     | 585 |      | 210 | ns |

| $t_{LLWL}$     | ALE 爲低電位到RD 或WR 爲低電位   | 200 | 300 | 75   | 175 | ns |

| $t_{\rm AVWL}$ | 位址到RD 或WR 爲低電位         | 203 |     | 91   |     | ns |

| $t_{RLAZ}$     | RD 爲低電位後到位址變爲浮接        |     | 0   |      | 0   | ns |

| $t_{\rm WHLH}$ | RD 或 WR 爲高電位到 ALE 爲高電位 | 43  | 123 | 21   | 66  | ns |

林銘波編著 --- 全華科技圖書公司

第8章 MCS-51硬體模式

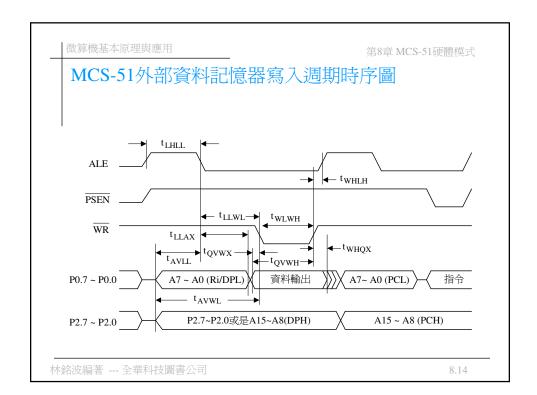

# AT89C51外部資料記憶器寫入週期之時序參數值 (12與24 MHz)

| 符號             | 參數                     | 12 MHz |     | 24 N | 單位  |    |

|----------------|------------------------|--------|-----|------|-----|----|

| 1寸5元           |                        | 最小值    | 最大値 | 最小値  | 最大値 | 里似 |

| $t_{LHLL}$     | ALE 脈波寬度               | 127    |     | 43   |     | ns |

| $t_{AVLL}$     | 位址成立到 ALE 爲低電位         | 28     |     | 28   |     | ns |

| $t_{\rm LLAX}$ | ALE 爲低電位後的位址持住時間       | 48     |     | 21   |     | ns |

| $t_{\rm WLWH}$ | WR 脈波寬度                | 400    |     | 150  |     | ns |

| $t_{\rm LLWL}$ | ALE 爲低電位到 RD 或 WR 爲低電位 | 200    | 300 | 75   | 175 | ns |

| $t_{\rm AVWL}$ | 位址到RD 或WR 爲低電位         | 203    |     | 91   |     | ns |

| $t_{QVWX}$     | 資料成立到WR 轉態             | 23     |     | 21   |     | ns |

| $t_{QVWH}$     | 資料成立到WR 爲高電位           | 433    |     | 172  |     | ns |

| $t_{WHQX}$     | WR 爲高電位後的資料持住時間        | 33     |     | 21   |     | ns |

| $t_{\rm WHLH}$ | RD 或 WR 爲高電位到 ALE爲高電位  | 43     | 123 | 21   | 66  | ns |

林銘波編著 --- 全華科技圖書公司

8.15

微算機基本原理與應用

第8章 MCS-51硬體模式

### AT89C51元件的規劃方式區分方法

|        | $V_{PP} = 12 \text{ V}$ | $V_{PP} = 5 \text{ V}$ |

|--------|-------------------------|------------------------|

|        | AT89C51                 | AT89C51                |

| 包裝上的註記 | XXXX                    | xxxx-5                 |

|        | yyww                    | yyww                   |

|        | (030H) = 1EH            | (030H) = 1EH           |

| 元件識別碼  | (031H) = 51H            | (031H) = 51H           |

|        | (032H) = FFH            | (032H) = 05H           |

第8章 MCS-51硬體模式

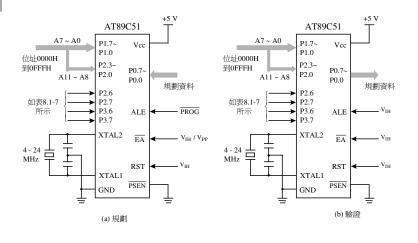

### AT89C51內部程式記憶器規劃與驗證

林銘波編著 --- 全華科技圖書公司

8.17

微算機基本原理與應用

第8章 MCS-51硬體模式

### AT89C51內部程式記憶器的規劃與驗證

| 模式     | 7    | RST | PSEN | ALE / PROG | EA / V <sub>PP</sub> | P2.6 | P2.7 | P3.6 | P3.7 |

|--------|------|-----|------|------------|----------------------|------|------|------|------|

| 寫入資料(規 | 見劃)  | Н   | L    | 7          | H/12 V               | L    | Н    | Н    | Н    |

| 讀取資料(縣 | 僉證)  | Н   | L    | Н          | Н                    | L    | L    | Н    | Н    |

| 鎖住位元   | 位元   | Н   | L    | 7          | H/12 V               | Н    | Н    | Н    | Н    |

| 1      |      |     |      |            |                      |      |      |      |      |

|        | 位元 2 | Н   | L    | 7          | H/12 V               | H    | Н    | L    | L    |

|        | 位元 3 | Н   | L    | 7          | H/12 V               | Н    | L    | Н    | L    |

| 晶片清除   |      | Н   | L    | 7          | H/12 V               | Н    | L    | L    | L    |

| 讀取識別碼  | į    | Н   | L    | Н          | Н                    | L    | L    | L    | L    |

林銘波編著 --- 全華科技圖書公司

第8章 MCS-51硬體模式

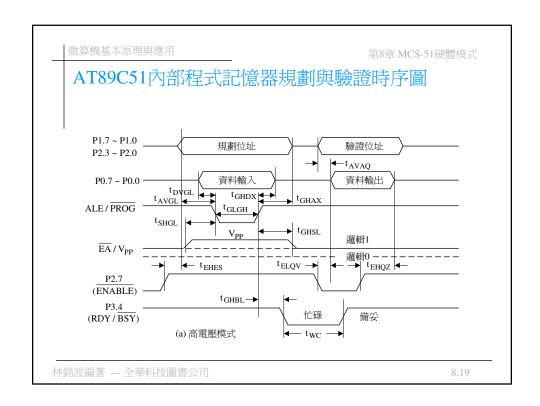

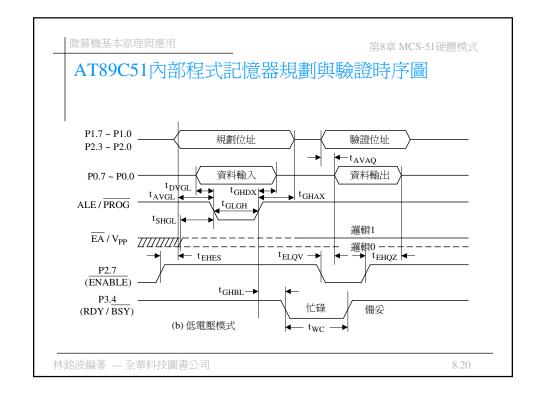

### AT89C51內部程式記憶器規劃與驗證時序參數值

| 符號                  | 參數                       | 最小値          | 最大値                   | 單位  |

|---------------------|--------------------------|--------------|-----------------------|-----|

| $V_{pp}$            | 規劃致能電壓(只使用在高電位模式)        | 11.5         | 12.5                  | V   |

| $I_{PP}$            | 規劃致能電流(只使用在高電位模式)        |              | 1.0                   | mA  |

| $1/t_{CLCL}$        | 時脈頻率                     | 4            | 24                    | MHz |

| $t_{AVGL}$          | 相對於PROG 爲低電位的位址設定時間      | $48t_{CLCL}$ |                       | ns  |

| $t_{GHAX}$          | 相對於PROG 爲低電位的位址持住時間      | $48t_{CLCL}$ |                       | ns  |

| $t_{\mathrm{DVGL}}$ | 相對於PROG 爲低電位的資料設定時間      | $48t_{CLCL}$ |                       | ns  |

| $t_{GHDX}$          | 相對於PROG 爲低電位的資料持住時間      | $48t_{CLCL}$ |                       | ns  |

| t <sub>EHSH</sub>   | P2.7 爲高電位後到VPP 的時間       | $48t_{CLCL}$ |                       | ns  |

| $t_{SHGL}$          | 相對於PROG 爲低電位的Vpp 設定時間    | 10           |                       | μs  |

| $t_{GHSL}$          | 相對於PROG 爲高電位的VPP 持住時間    | 10           |                       | μs  |

| $t_{GLGH}$          | PROG 脈波寬度                | 1            | 110                   | μs  |

| $t_{AVAQ}$          | 位址到資料的成立時間               |              | $48t_{CLCL}$          | ns  |

| $t_{ELQV}$          | P2.7 爲低電位到資料成立的時間        |              | $48t_{\mathrm{CLCL}}$ | ns  |

| $t_{ EHQV}$         | P2.7 爲低電位到資料浮接的時間        |              | $48t_{\rm CLCL}$      | ns  |

| $t_{GHBL}$          | PROG 爲高電位到 BUSY 變爲低電位的時間 |              | 1.0                   | μs  |

| $t_{WC}$            | 位元組寫入週期                  |              | 2.0                   | ms  |

林銘波編著 --- 全華科技圖書公司

8.21

微算機基本原理與應用

第8章 MCS-51硬體模式

### 程式記憶器的規劃

#### AT89C51 程式記憶器規劃程序

#### BEGIN:

- 1. 輸入適當的位址信號,選定欲規劃的位置。

- 2. 在資料匯流排,輸入適當的資料信號。

- 3. 啓動適當組合的控制信號。

- 4. 若爲高電壓規劃模式,提升 $EA/V_{PP}$ 爲 12V。

- 5. 啟動 ALE / PROG 脈波一次,以寫入一個位元組資料於記憶器中,或是規劃鎖住位元。

- 6. 重複上述步驟 1 到 5 的動作,適當的改變位址與資料信號值,直到整個記憶器或是資料檔耗盡爲止。

#### **END**

第8章 MCS-51硬體模式

## MCS-51鎖住位元的功能

| 模式 | LB1 | LB2 | LB3 | 保護功能                                                                  |

|----|-----|-----|-----|-----------------------------------------------------------------------|

| 1  | U   | U   | U   | 不具有程式鎖住功能。                                                            |

| 2  | P   | U   | U   | 在重置後取樣並且鎖住EA 信號,禁止進一步的規劃內部程式記憶器;由外部程式記憶器執行的 MOVC 指令,禁止自內部程式記憶器中讀取指令碼。 |

| 3  | P   | P   | U   | 與模式 2 相同,並且禁止程式記憶器<br>的驗證。                                            |

| 4  | P   | P   | P   | 與模式3相同,並且禁止外部執行。                                                      |

林銘波編著 --- 全華科技圖書公司

8.23

微算機基本原理與應用

第8章 MCS-51硬體模式

### AT89C51輸入與輸出電氣特性

| $V_{IL} = 0.9 \text{ V(max)}$ | $V_{IH} = 1.9 \text{ V(min)}$ | $V_{OL} = 0.45 \text{ V(max)}$ | $V_{OH} = 2.4 \text{ V(min)}$   |

|-------------------------------|-------------------------------|--------------------------------|---------------------------------|

| $I_{\rm IL}$ = - 50 $\mu A$   | $I_{IH} = -1 \mu A$           | $I_{OL} = 1.6 \text{ mA(min)}$ | $I_{OH} = -60 \mu\text{A(min)}$ |

第8章 MCS-51硬體模式

## AT89C51對各種邏輯族系的元件之扇出數目

|            | I <sub>IL</sub> | I <sub>IH</sub> | I <sub>OL</sub> | I <sub>OH</sub> | AT89C51 的扇出 |

|------------|-----------------|-----------------|-----------------|-----------------|-------------|

| 74LSxx     | -0.4 mA         | 20 μΑ           | 8 mA            | -0.4 mA         | 3           |

| 74Fxx      | -0.6 mA         | 20 μΑ           | 20 mA           | -1.0 mA         | 2           |

| 74Sxx      | -2.0 mA         | 50 μA           | 20 mA           | -1.0 mA         | 1           |

| 74ALSxx    | -0.2 mA         | 20 μA           | 4.0 mA          | -0.4 mA         | 3           |

| 74HC/HCTxx | -0.1 μA         | 0.1 μΑ          | 4 mA            | -4 mA           | 600         |

林銘波編著 --- 全華科技圖書公司

8.25

微算機基本原理與應用

第8章 MCS-51硬體模式

### 各種族系的138/373元件特性資料

| 373           | 74F | 74HCT | 74LS | 74S | 74AS | 74ALS |

|---------------|-----|-------|------|-----|------|-------|

| 設定時間(min)(ns) | 2   | 13    | 5    | 0   | 2    | 10    |

| 持住時間(min)(ns) | 3   | 10    | 20   | 10  | 3    | 7     |

| 傳播延遲(max)(ns) | 13  | 44    | 30   | 18  | 11.5 | 23    |

| 138           |     |       |      |     |      |       |

| 傳播延遲(max)(ns) | 8.5 | 45    | 41   | 12  | 10   | 22    |

第8章 MCS-51硬體模式

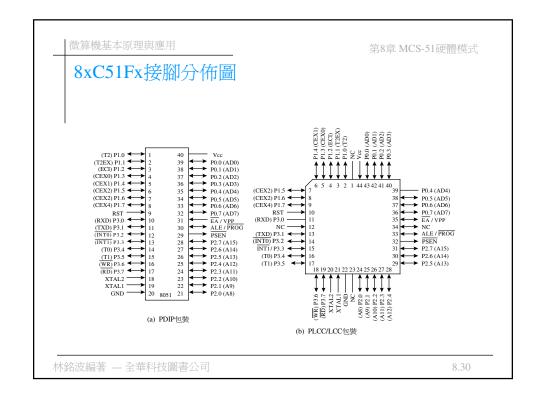

### 8xC51Fx I/O埠1的副功能

| 埠位元  | 副功能                          |

|------|------------------------------|

| P1.0 | T2(定時器2的外部計數輸入)              |

| P1.1 | T2EX(定時器 2 的捕捉、重新載入觸發、及方向控制) |

| P1.2 | ECI (PCA 的外部計數輸入)            |

| P1.3 | CEX0 (比較與捕捉模組 0 的外部 I/O)     |

| P1.4 | CEX1 (比較與捕捉模組 1 的外部 I/O)     |

| P1.5 | CEX2 (比較與捕捉模組 2 的外部 I/O)     |

| P1.6 | CEX3 (比較與捕捉模組 3 的外部 I/O)     |

| P1.7 | CEX4 (比較與捕捉模組 4 的外部 I/O)     |

林銘波編著 --- 全華科技圖書公司

第8章 MCS-51硬體模式

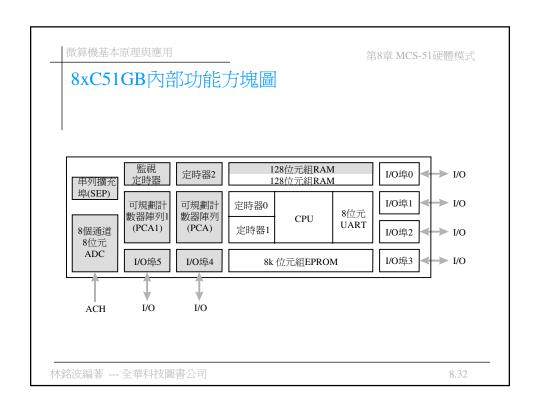

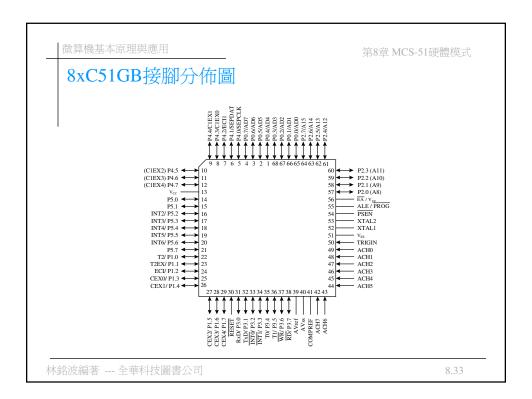

### 8xC51GB I/O埠1的副功能

| 埠位元  | 副功能                          |

|------|------------------------------|

| P1.0 | T2 (定時器 2 的外部計數輸入)           |

| P1.1 | T2EX(定時器 2 的捕捉、重新載入觸發、及方向控制) |

| P1.2 | ECI (PCA 的外部計數輸入)            |

| P1.3 | CEX0 (比較與捕捉模組 0 的外部 I/O)     |

| P1.4 | CEX1 (比較與捕捉模組 1 的外部 I/O)     |

| P1.5 | CEX2 (比較與捕捉模組 2 的外部 I/O)     |

| P1.6 | CEX3 (比較與捕捉模組 3 的外部 I/O)     |

| P1.7 | CEX4 (比較與捕捉模組 4 的外部 I/O)     |

林銘波編著 --- 全華科技圖書公司

第8章 MCS-51硬體模式

## 8xC51GB I/O埠3的副功能

| 埠位元  | 副功能              |

|------|------------------|

| P3.0 | RxD (串列輸入埠)      |

| P3.1 | TxD (串列輸出埠)      |

| P3.2 | INTO (外部中斷輸入 0)  |

| P3.3 | INT1 (外部中斷輸入 1)  |

| P3.4 | T0 (定時器 0 外部輸入)  |

| P3.5 | T1 (定時器 1 外部輸入)  |

| P3.6 | WR (外部資料記憶器寫入控制) |

| P3.7 | RD (外部資料記憶器讀取控制) |

林銘波編著 --- 全華科技圖書公司

8.35

微算機基本原理與應用

第8章 MCS-51硬體模式

### 8xC51GB I/O埠4的副功能

| 埠位元  | 副功能                            |

|------|--------------------------------|

| P4.0 | SEPCLK (SEP 的外部時脈輸入)           |

| P4.1 | SEPDAT (SEP 的資料 I/O)           |

|      | ECII (PCA1 的外部計數輸入)            |

| P4.3 | C1EX0 (PCA1 比較與捕捉模組 0 的外部 I/O) |

| P4.4 | C1EX1 (PCA1 比較與捕捉模組 1 的外部 I/O) |

|      | C1EX2 (PCA1 比較與捕捉模組 2 的外部 I/O) |

| P4.6 | C1EX3 (PCA1 比較與捕捉模組 3 的外部 I/O) |

| P4.7 | C1EX4 (PCA1 比較與捕捉模組 4 的外部 I/O) |

林銘波編著 --- 全華科技圖書公司

第8章 MCS-51硬體模式

## 8xC51GB I/O埠5的副功能

| 埠位元  | 副功能            |

|------|----------------|

| P5.2 | 外部中斷要求輸入(INT2) |

| P5.3 | 外部中斷要求輸入(INT3) |

| P5.4 | 外部中斷要求輸入(INT4) |

| P5.5 | 外部中斷要求輸入(INT5) |

| P5.6 | 外部中斷要求輸入(INT6) |

林銘波編著 --- 全華科技圖書公司