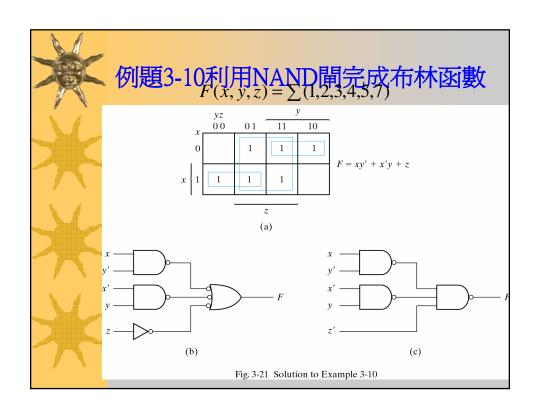

### 布林函數以二階NAND閘實現之步驟

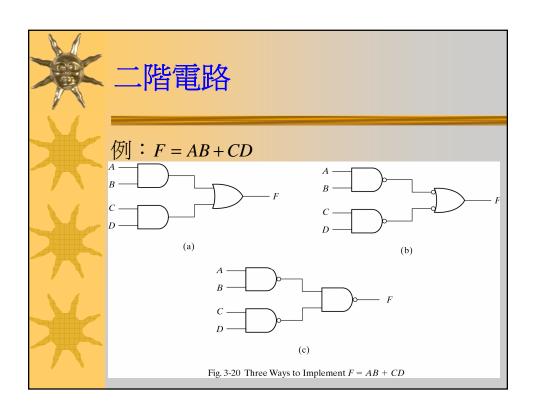

- ★將函數簡化成積項和的形式。

- \*將表示式中至少含有2個字元的每一個 積項用一個NAND閘來表示。每個NAND閘 的輸入為每一項中的變數,由此構成邏 輯電路圖的第一階邏輯閘。

## 布林函數以二階NAND閘實現之步驟

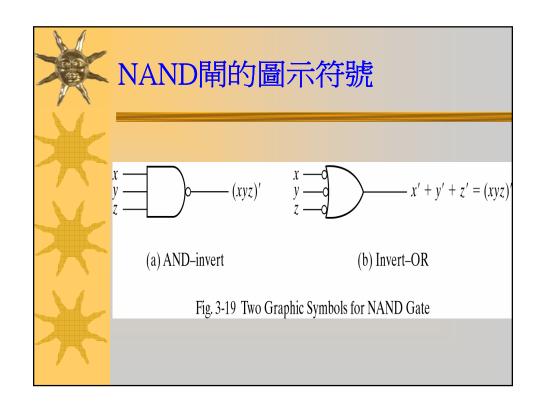

- \*在第二階的部分使用單一個AND-invert 或invert-OR的閘圖示符號來表示,而 其輸入來自第一階閘的輸出。

- \*若函數中有任一項只含一個文字(變數),則在第一階需要一個反相器,然而,若將單一個字元取補數,則可以直接將它連接到第二階NAND閘的一個輸入。

# 3-8 互斥-OR函數

#### ★互斥-OR

$$x \oplus y = xy' + x'y$$

$$x \oplus 0 = x$$

$$x \oplus 1 = x'$$

$$x \oplus x = 0$$

$$x \oplus x' = 1$$

$$x \oplus y' = x' \oplus y = (x \oplus y)'$$

#### \*全等

$$(x \oplus y)' = (xy' + x'y)'$$

$$= (x' + y)(x + y')$$

$$= xy + x'y'$$

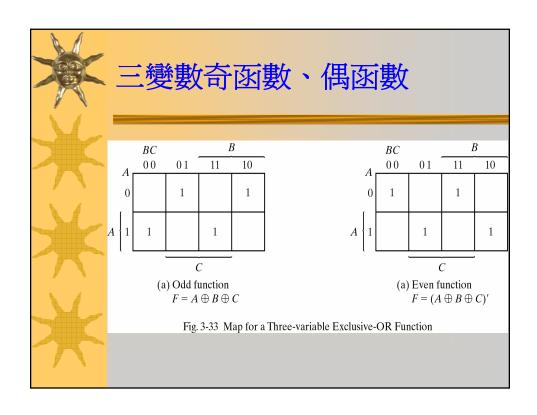

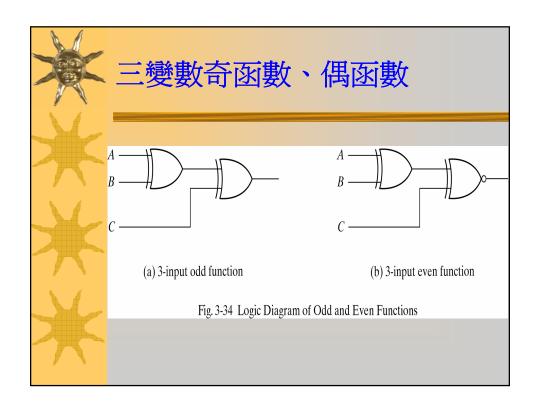

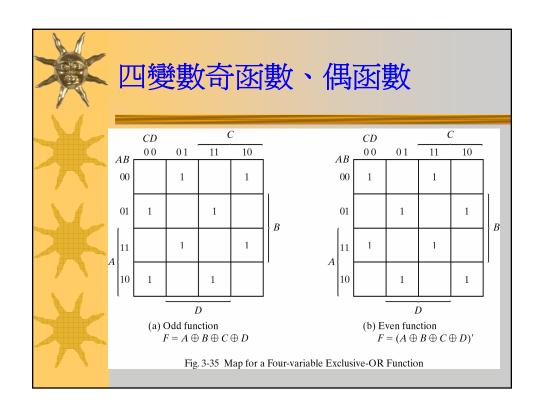

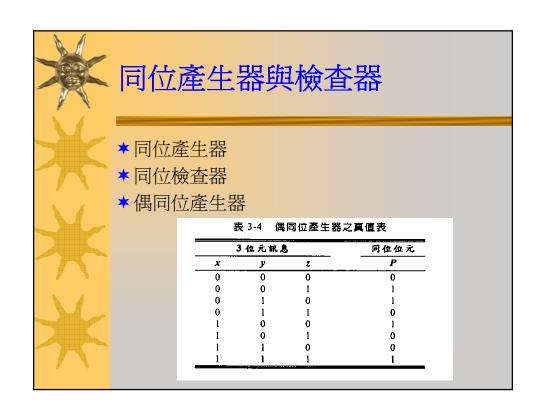

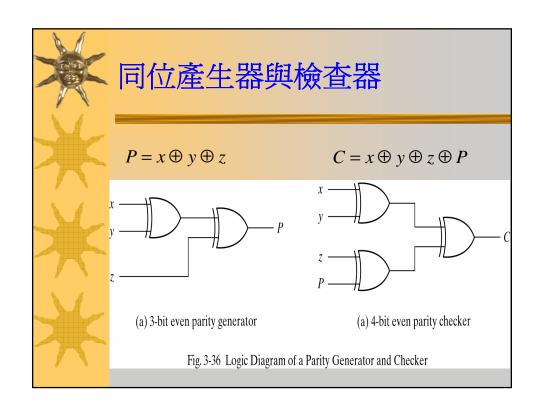

# 奇函數、偶函數

- ★奇函數---三個或更多個變數中,奇數個變數等於1則函數等於1

- ★偶函數---三個或更多個變數中,偶數個 變數等於1則函數等於1

## 3-9 硬體描述語言

- ★邏輯模擬(logic simulation)

- **★**邏輯合成(logic synthesis)

- **★**測試平台(test bench)

# 模組表示法

```

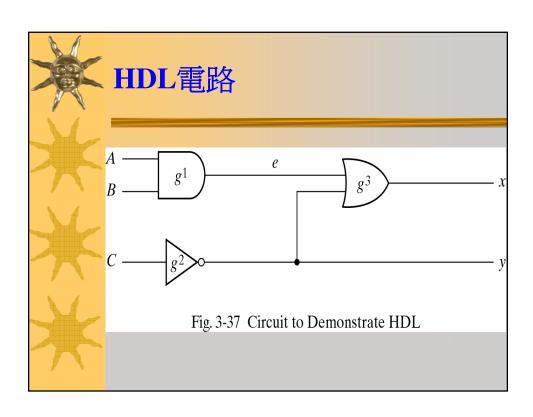

*HDL 範例3 -1

```

```

//Description of the simple circuit of Fig. 3-37

module smpl_circuit(A,B,C,x,y);

input A,B,C;

output x,y;

wire e;

and g1(e,A,B);

not g2(y, C);

```

endmodule

or g3(x,e,y);

### HDL 範例 3-3 (模擬一個具有延遲電路的測試平台)

```

//Stimulus for simple circuit

module stimcrct;

reg A,B,C;

wire x,y;

circuit_with_delay cwd(A,B,C,x,y);

initial

```

### HDL 範例 3-3 (模擬一個具有延遲電路的測試平台)

### begin

A = 1'b0; B = 1'b0; C = 1'b0; #100 A = 1'b1; B = 1'b1; C = 1'b1; #100 \$finish; end endmodule

### HDL 範例 3-3 (模擬一個具有延遲電路的測試平台)

```

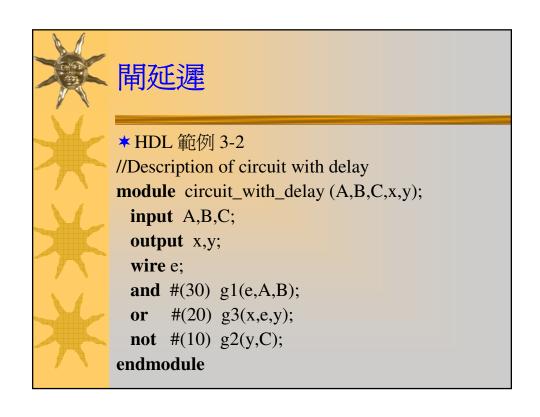

//Description of circuit with delay

module circuit_with_delay (A,B,C,x,y);

input A,B,C;

output x,y;

wire e;

and #(30) g1(e,A,B);

or #(20) g3(x,e,y);

not #(10) g2(y,C);

endmodule

```

## 布林表示式

x = A + BC + B'Dy = B'C + BC'D'

#### \*HDL 範例 3-4

//Circuit specified with Boolean equations

module circuit\_bln (x,y,A,B,C,D);

input A,B,C,D;

output x,y;

assign x = A | (B & C) | (~B & C);

assign y = (~B & C) | (B & ~C & ~D);

endmodule

## 使用者定義的原始值

- **★使用關鍵字 primitive** 作宣告

- ★只可以有一個輸出且此輸出必須列在埠 名單的第一個還有必須用關鍵字output來 宣告。

- \*輸入數目不限制,至於它們在input宣告中的順序則必須與它們在下面表中所給值的順序相同。

# 使用者定義的原始值(UDP)

- \*真值表必須在關鍵字table及endtable之間。

- \*輸入值依順序列出,用冒號(:)代表結束,輸出通常是每一列的最後一個記錄,後面跟著是一個分號(;)。

- \*最後用關鍵字endprimitive作結束。

```

HDL 範例 3-5

(利用一個真值表來定義UDP)

//User defined primitive(UDP)

primitive crctp (x,A,B,C);

output x;

input A,B,C;

//Truth table for x(A,B,C) = Minterms (0,2,4,6,7)

table

```

```

HDL 範例 3-5

(利用一個真值表來定義UDP)

// A B C: x (Note that this is only a comment)

0 0 0: 1;

0 0 1: 0;

0 1 0: 1;

0 1 1: 0;

1 0 0: 1;

1 0 1: 0;

1 1 1: 1;

endtable

endprimitive

```

## HDL 範例 3-5 (利用一個真值表來定義UDP)

```

//Instantiate primitive

module declare_crctp;

reg x,y,z;

wire w;

crctp (w,x,y,z);

endmodule

```